Aš biški domiuosiu senais kompais, o ten dažnai naudojamos programuojamos logikos mikroschemos (PAL/TIBPAL/GAL/PALCE). Šios mikroschemos, ypač senos laidos, labai kaista ir net kartais nuo to kaitimo susidefektuoja. Todėl kartais jas reikia pakeisti “naujom” PALCE ar GAL mikroschemom. Visa bėda- nežinom mikroschemos turinio. Kartais “fuse” failai randami internete, kartais net būna “lygtys”. Kartais galima atstatyti turinį pagal prietaiso schemą (taip atstačiau ATARI 1200 čipą). Tačiau tai suveikia ne visada.

GAL ir PALCE čipai perrašomi. Todėl juos galima lupinėti iš senų plokščių ir panaudoti iš naujo.

Internete yra metodas, kad paprastas mikroschemas (be registrų) galima atburti naudojant paprastą “brute force” t.y. išbandant visus variantus ant kojyčių. PAL mikroschema prijungiama kaip 27C020 ir nuskaitoma kaip paprastas EPROM ir gautas “rom dump” sumaitinamas specialiai programai “pa.exe”.

Jei PAL/GAL mikroschema neturi viduje registrų ir (kas svarbu!) neturi viduje užciklintos logikas “ala” registras, tai viskas veikia. Deja, tos mikroschemos kurios man buvo svarbios buvo TIBPAL16L8 – gryna logika, bet “užciklintos” ir man nepavyko jas “nulaužti”…

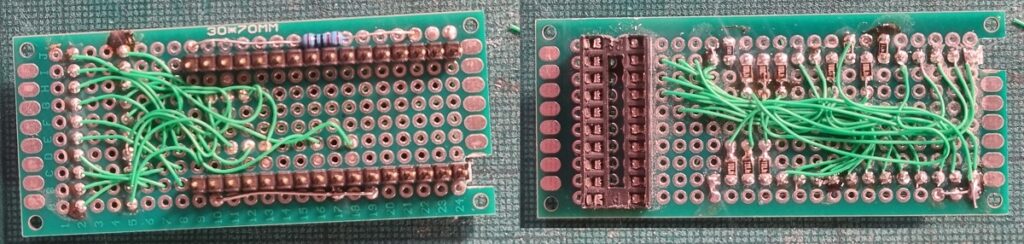

Taip atrodo PAL16L8 į 27C020 adapteris.

Taigi, jei netyčia turit Amiga 2000 1Mb DRAM plokštės jungiamos į CPU slotą schemą ar PAL formules, pasidalinkit 🙂 Nes dabar atminties išpėtimas net pradeda smirdėti nuo karščio.